- 您现在的位置:买卖IC网 > Sheet目录364 > SST49LF080A-33-4C-WHE-T (Microchip Technology)IC FLASH SER LPC 8MBIT 32TSOP

8 Mbit LPC Flash

A Microchip Technology Company

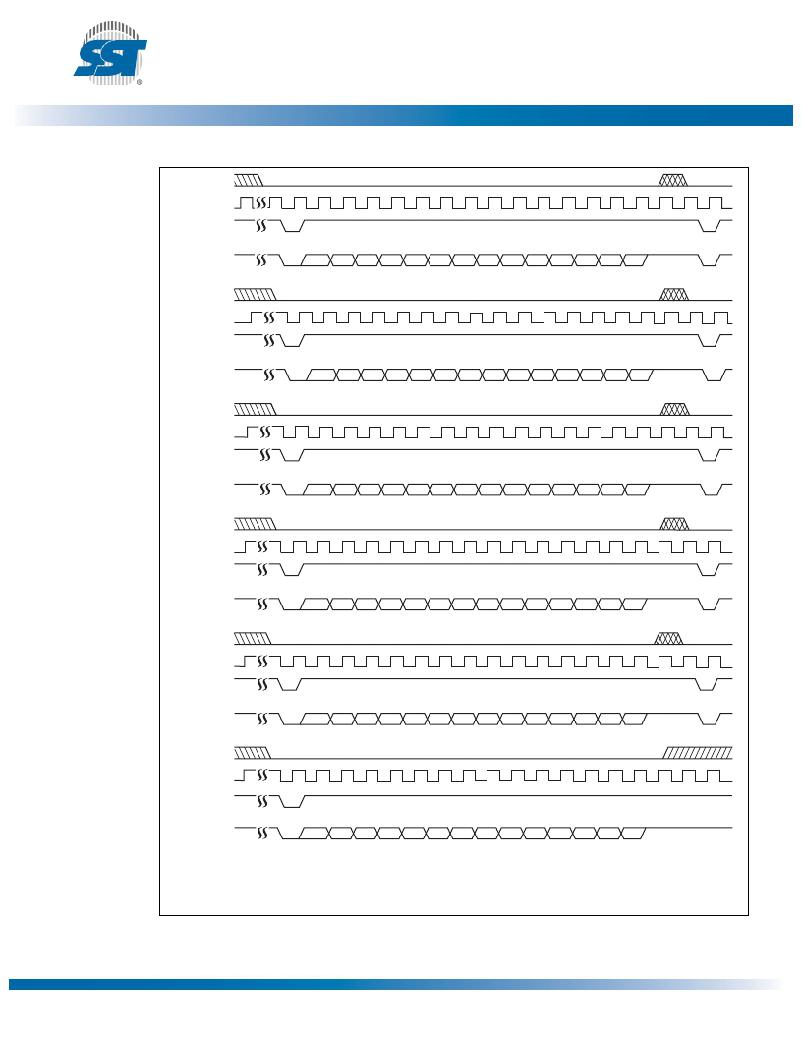

CE#

LCLK

LFRAME#

SST49LF080A

Data Sheet

1st Start

Memory

Write

Cycle

Address1

Data

TAR

Sync

Start next

Command

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

0101b

0101b

0101b

0101b

1010b

1010b

1111b

Tri-State 0000b

TAR

1 Clock 1 Clock

Load Address YYYY 5555H in 8 Clocks

Load Data AAH in 2 Clocks 2 Clocks

1 Clock

1 Clock

Write the 1st command to the device in LPC mode.

CE#

LCLK

LFRAME#

2nd Start

Memory

Write

Cycle

Address1

Data

TAR

Sync

Start next

Command

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

0010b

1010b

1010b

1010b

0101b

0101b

1111b

Tri-State

0000b

TAR

1 Clock 1 Clock

Load Address YYYY 2AAAH in 8 Clocks

Load Data 55H in 2 Clocks

2 Clocks

1 Clock

1 Clock

Write the 2nd command to the device in LPC mode.

CE#

LCLK

LFRAME#

3rd Start

Memory

Write

Cycle

Address1

Data

TAR

Sync

Start next

Command

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

0101b

0101b

0101b

0101b

0000b

1000b

1111b Tri-State

0000b

TAR

1 Clock 1 Clock

Load Address YYYY 5555H in 8 Clocks

Load Data 80H in 2 Clocks

2 Clocks

1 Clock

1 Clock

Write the 3rd command to the device in LPC mode.

CE#

LCLK

LFRAME#

4th Start

Memory

Write

Cycle

Address1

Data

TAR

Sync

Start next

Command

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

0101b

0101b

0101b

0101b

1010b

1010b

1111b

Tri-State

0000b

TAR

1 Clock 1 Clock

Load Address YYYY 5555H in 8 Clocks

Load Data AAH in 2 Clocks 2 Clocks

1 Clock

1 Clock

Write the 4th command to the device in LPC mode.

CE#

LCLK

LFRAME#

5th

Memory

Write

Cycle

Address1

Data

TAR

Sync

Start next

Command

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

0010b

1010b

1010b

1010b

0101b

0101b

1111b

Tri-State

0000b

TAR

1 Clock 1 Clock

Load Address YYYY 2AAAH in 8 Clocks

Load Data 55H in 2 Clocks

2 Clocks

1 Clock

1 Clock

Write the 5th command to the device in LPC mode.

CE#

LCLK

Internal

erase start

LFRAME#

6th Start

Memory

Write

Cycle

Address1

Data

TAR

Sync

Internal

erase start

LAD[3:0]

0000b

011Xb

A[31:28] A[27:24] A[23:20] A[19:16]

BAX

XXXXb

XXXXb

XXXXb

0000b

0101b

1111b

Tri-State 0000b

TAR

1 Clock 1 Clock

Load Block Address in 8 Clocks

Load Data “50” in 2 Clocks

2 Clocks

1 Clock

Write the 6th command (target sector to be erased) to the device in LPC mode.

BAX = Block Address

Note: 1. Address must be within memory address range specified in Table 4.

Figure 11: Block-Erase Command Sequence (LPC Mode)

1235 F10.0

?2011 Silicon Storage Technology, Inc.

25

DS25086A

11/11

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SST49LF160C-33-4C-NHE

IC FLASH SER LPC 16MBIT 32PLCC

ST40

DIAC 35-45V BILATERAL TRIG DO214

STRIKER

SURGE SUPPRESSR 120V 7OUT 6'CORD

SUPER-7

SURGE SUPPRESSOR 7 OUT 7' CORD

SUPER6TEL12

SURGE SUPPR 7OUT 12'CORD W/RJ11

SUPER6TEL

SURGE SUPPRESSOR 7OUT W/TEL

SUPER7COAX

SURGE SUPPRESSOR 7 OUT W/COAX

SUPER7TEL15

SURGE SUPPR 7OUT 15'CORD W/RJ11

相关代理商/技术参数

SST49LF160C

制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:16 Mbit LPC Flash

SST49LF160C334CNHE

制造商:Microchip Technology Inc 功能描述:

SST49LF160C-33-4C-NHE

功能描述:闪存 16M (2Mx8) 33MHz 3.0-3.6V Commercial RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel

SST49LF160C-33-4C-NHE_

制造商:Microchip Technology Inc 功能描述:

SST4H-D

功能描述:电缆束带 Cable Tie, 2-Piece, 14.8"L (376mm), Ligh RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4H-D0

功能描述:电缆束带 14.8" BLK CABLE TIE RELEAS WEATHER RES RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4H-D30

功能描述:电缆束带 Cable Tie, 2-Piece, 14.8"L (376mm), Ligh RoHS:否 制造商:Phoenix Contact 产品:Cable Tie Mounts 类型:Adhesive 颜色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 长度:19 mm 宽度:19 mm 抗拉强度:

SST4HH-D

制造商:Panduit Corp 功能描述: